- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Warstwy epitaksjalne: podstawa zaawansowanych urządzeń półprzewodnikowych

Rysunek 1: Ilustruje korelację pomiędzy stężeniami domieszki, grubością warstwy i napięciem przebicia dla urządzeń jednobiegunowych.

Przygotowanie warstw epitaksjalnych SiC obejmuje przede wszystkim techniki takie jak wzrost przez odparowanie, epitaksja w fazie ciekłej (LPE), epitaksja z wiązek molekularnych (MBE) i chemiczne osadzanie z fazy gazowej (CVD), przy czym CVD jest dominującą metodą masowej produkcji w fabrykach.

Tabela 1: Zawiera przegląd porównawczy głównych metod przygotowania warstwy epitaksjalnej.

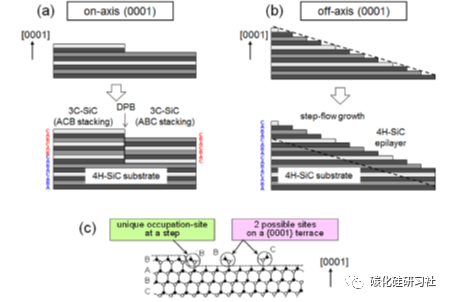

Przełomowe podejście obejmuje wzrost na podłożach poza osią pod określonym kątem nachylenia, jak pokazano na rysunku 2(b). Metoda ta znacznie zwiększa gęstość stopni, jednocześnie zmniejszając ich wielkość, ułatwiając zarodkowanie przede wszystkim w miejscach skupień stopni, a tym samym umożliwiając warstwie epitaksjalnej doskonałe odwzorowanie sekwencji układania podłoża, eliminując współistnienie politypów.

Rysunek 2: Demonstruje proces fizyczny kontrolowanej etapowo epitaksji w 4H-SiC.

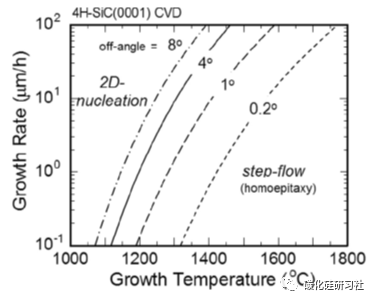

Figura 3: Pokazuje krytyczne warunki wzrostu CVD w epitaksji kontrolowanej etapowo dla 4H-SiC.

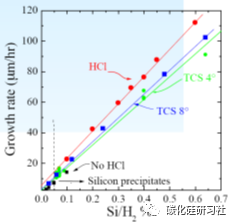

Rysunek 4: Porównuje tempo wzrostu epitaksji 4H-SiC przy różnych źródłach krzemu.

W dziedzinie zastosowań niskiego i średniego napięcia (np. urządzenia 1200 V) technologia epitaksji SiC osiągnęła dojrzały etap, oferując stosunkowo doskonałą jednorodność grubości, stężenia domieszki i rozkładu defektów, odpowiednio spełniając wymagania dla SBD niskiego i średniego napięcia , MOS, urządzenia JBS i inne.

Jednak dziedzina wysokiego napięcia nadal stwarza poważne wyzwania. Na przykład urządzenia o napięciu znamionowym 10000 V wymagają warstw epitaksjalnych o grubości około 100 μm, ale warstwy te wykazują znacznie gorszą grubość i jednorodność domieszkowania w porównaniu z ich odpowiednikami niskonapięciowymi, nie wspominając o szkodliwym wpływie defektów trójkątnych na ogólną wydajność urządzenia. Zastosowania wysokiego napięcia, które zwykle faworyzują urządzenia bipolarne, również nakładają rygorystyczne wymagania dotyczące żywotności nośników mniejszościowych, co wymaga optymalizacji procesu w celu poprawy tego parametru.

Obecnie na rynku dominują płytki epitaksjalne SiC o średnicy 4 i 6 cali, przy stopniowym zwiększaniu się udziału płytek epitaksjalnych SiC o dużej średnicy. Rozmiar płytek epitaksjalnych SiC jest zasadniczo zdeterminowany wymiarami podłoży SiC. Ponieważ 6-calowe podłoża SiC są obecnie dostępne na rynku, przejście z 4-calowej do 6-calowej epitaksji SiC postępuje stale.

W miarę postępu technologii wytwarzania podłoży SiC i zwiększania się mocy produkcyjnych, koszt podłoży SiC stopniowo maleje. Biorąc pod uwagę, że substraty stanowią ponad 50% kosztów płytek epitaksjalnych, oczekuje się, że spadające ceny substratów doprowadzą do niższych kosztów epitaksji SiC, obiecując w ten sposób lepszą przyszłość branży.**