- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Co to jest proces CMP

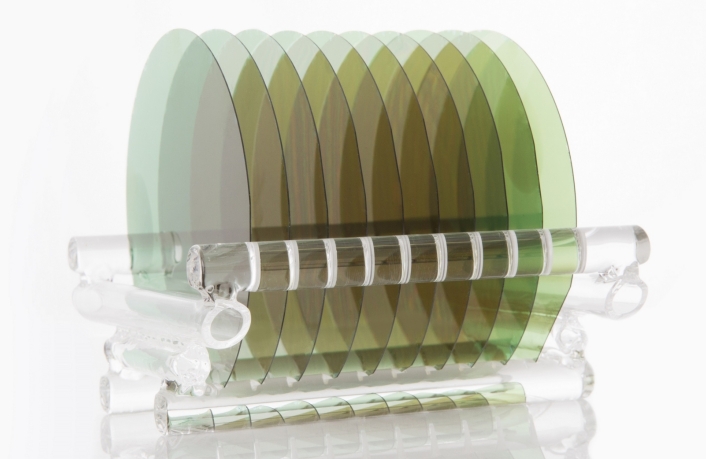

W produkcji półprzewodników płaskość na poziomie atomowym jest zwykle używana do opisania globalnej płaskościopłatekz jednostką nanometrów (nm). Jeżeli wymóg globalnej płaskości wynosi 10 nanometrów (nm), jest to równoważne maksymalnej różnicy wysokości wynoszącej 10 nanometrów na powierzchni 1 metra kwadratowego (globalna płaskość 10 nm jest równoważna różnicy wysokości pomiędzy dowolnymi dwoma punktami na placu Tiananmen o powierzchnia 440 000 metrów kwadratowych nie przekraczająca 30 mikronów.) A chropowatość powierzchni jest mniejsza niż 0,5 um (w porównaniu do włosa o średnicy 75 mikronów, odpowiada to jednej 150 000 włosa). Wszelkie nierówności mogą spowodować zwarcie, przerwę w obwodzie lub wpłynąć na niezawodność urządzenia. To wymaganie dotyczące wysokiej precyzji płaskości należy osiągnąć za pomocą procesów takich jak CMP.

Zasada procesu CMP

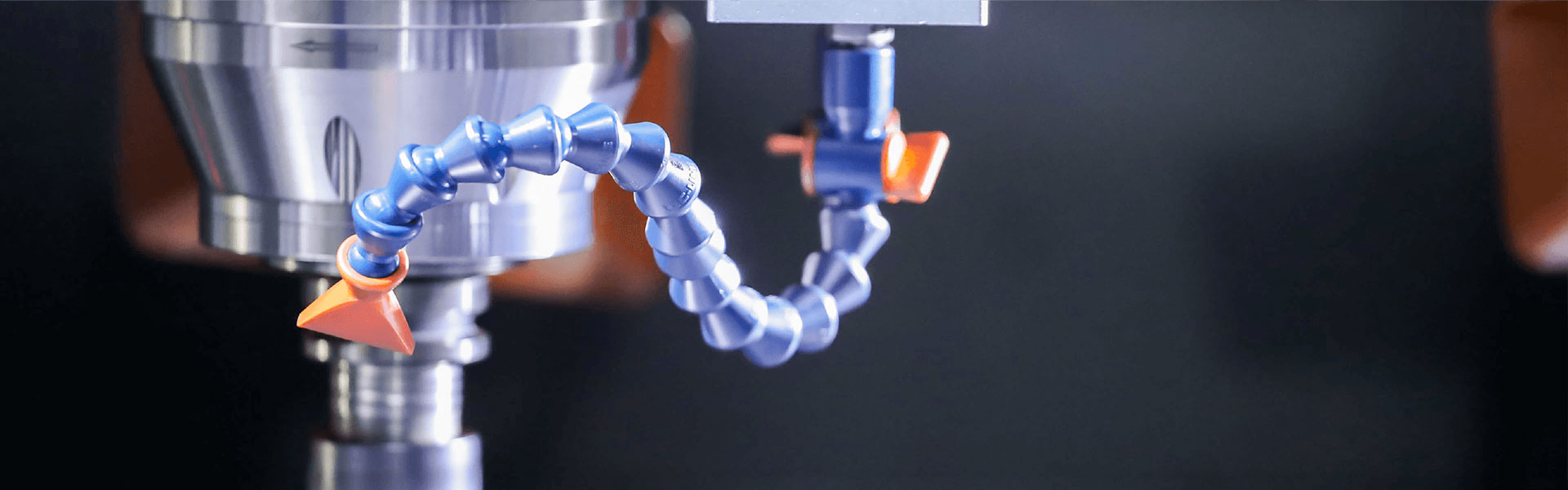

Polerowanie chemiczno-mechaniczne (CMP) to technologia stosowana do spłaszczania powierzchni płytki podczas produkcji chipów półprzewodnikowych. W wyniku reakcji chemicznej pomiędzy płynem polerskim a powierzchnią płytki powstaje łatwa w obróbce warstwa tlenku. Następnie powierzchnię warstwy tlenku usuwa się poprzez mechaniczne szlifowanie. Po przeprowadzeniu naprzemiennie wielu działań chemicznych i mechanicznych powstaje jednolita i płaska powierzchnia płytki. Reagenty chemiczne usunięte z powierzchni płytki są rozpuszczane w przepływającej cieczy i odprowadzane, dlatego proces polerowania CMP obejmuje dwa procesy: chemiczny i fizyczny.